Circuit

intégré complet

L'idée d'intégration sur une même surface de silicium de

plusieurs composants réalisant une fonction complexe a très vite

suivi l'invention du transistor. En fait dès 1953 l'industrie aéronautique

américaine demandait aux fabricants de transistors de préparer

des circuits complets à partir de plaquettes de silicium et les premiers

prototypes chez Texas Instruments ou Westinghouse virent le jour vers 1958.

Mais il fallut attendre encore quelques années avant la commercialisation

d'un circuit fiabilisé et de caractéristiques reproductibles.

Pendant la seconde guerre mondiale le principe de l'amplificateur différentiel,

alors réalisé avec des tubes triodes, avait été

imaginé, c'est donc tout naturellement que le premier circuit intégré

commercialisé a été l'amplificateur opérationnel

réalisé par Bob

Widlar chez Fairchild Semiconductor en 1965 (il s'agissait du µA709

dont les premiers exemplaires valaient plus de 200$, alors qu'aujourd'hui on

trouve pour une fraction d'euro des composants plus performants chez n'importe

quel distributeur). Les circuits, dits logiques TTL, apparurent dans la foulée

et en 1968 on vit paraître les premiers databooks de ces composants.

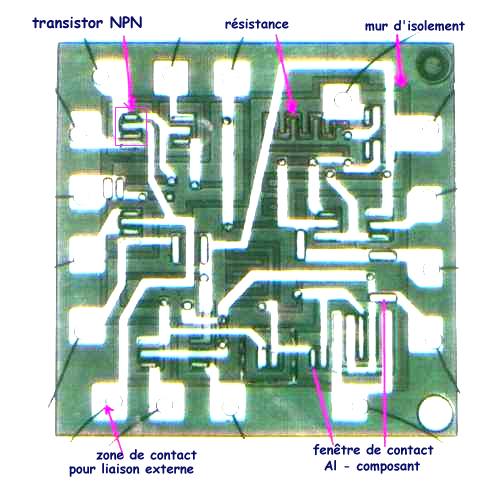

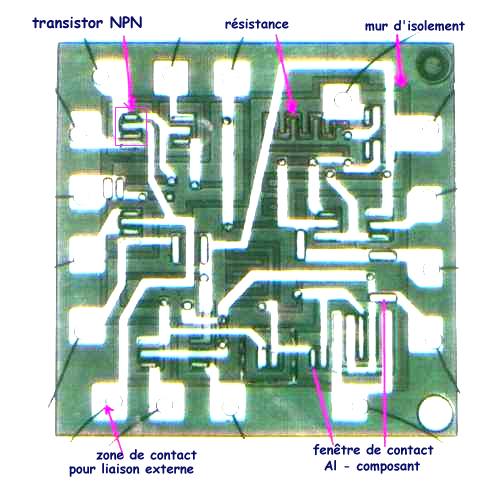

La figure ci-dessous présente à titre d'illustration une photographie

d'un circuit de type amplificateur opérationnel relativement ancien sur

laquelle on peut distinguer aisément nombre de transistors, en particulier

NPN, des résistances de type base et les murs d'isolement qui encerclent

les éléments devant être isolés les uns des autres,

ainsi bien évidemment que les couches d'aluminium assurant les liaisons

indispensables entre ces éléments entre eux ou avec l'extérieur.

Notons que sur les amplis récents on retrouve des structures semblables,

mais la miniaturisation est telle qu'il est quasiment impossible d'y reconnaitre

comme sur la figure ci-dessous des éléments distincts. Pour mémoire

le circuit ci-dessous fait 2.54mm de côté.

amplificateur opérationnel classique avant encapsulation (grossissement

environ 4000)

amplificateur opérationnel classique avant encapsulation (grossissement

environ 4000)

Notons que ces divers éléments sont visibles en raison de l'épaisseur

différente d'oxyde recouvrant les différentes zones et donc du

processus différent de réflexion de la lumière. Sur les

couches d'aluminium on distingue très facilement les dénivellations

en certains points de contact avec des ouvertures dans la couche d'oxyde protégeant

tout le circuit.

Précisons enfin que cet exemple est donné à titre pédagogique.

Dans les composants récents les dimensions sont infiniment réduites,

ainsi en 2006 la compagnie INTEL a mis en oeuvre industriellement dans plusieurs

usines des procédés ultra miniaturisés lui permettant de

réaliser des transistors de 65nm soit une réduction linéaire

d'un facteur 400000 par rapport au circuit ci-dessus. Un simple calcul montre

que cela correspond sensiblement à une réduction de taille d'un

facteur 2 tous les 2 ans depuis 40 ans ce qui a été rendu possible

par une amélioration gigantesque de la précision de tous les appareils

intervenant dans la chaîne de production. Sachant qu'un atome a un diamètre

de 0.3nm environ il est intuitif de penser que l'on va bientôt atteindre

un seuil critique au delà duquel il ne sera plus possible de continuer

à réduire les dimensions des composants. On envisage alors de

changer complètement de technologies pour réaliser des nanosystèmes

qui ne seront plus basés sur le seul silicium, mais plus vraisemblablement

sur une structure particulière à base de carbone, mais il faut

compter encore de nombreuses années avant que ces technologies prometteuses

en laboratoire soient suffisamment fiables et peu coûteuses pour passer

au domaine industriel. Nous y reviendrons dans un avenir plus ou moins proche.

Spécificités du micro-usinage

La réalisation de microcapteurs intégré implique souvent

deux parties différentes :

- d'une part, la réalisation du transducteur

qui comporte le plus souvent des éléments de type résistance

base, parfois quelques éléments actifs qui seront réalisés

selon les procédés vus ci-dessus et n'appellent donc pas de

commentaire particulier. Sinon que le plus souvent on dispose d'une surface

importante sur laquelle le positionnement des éléments ne

résulte pas seulement de considérations topologiques telles

que celles définissant les implantations de composants comme dans

l'amplificateur opérationnel ci-dessus, avec l'objectif d'utiliser

le moins de surface possible, mais plus souvent le positionnement dépend

du type de capteur. Ainsi le pont de résistances d'un capteur de

pression sera positionné en des emplacements où la membrane

de silicium présente les déformations optimales.

- d'autre part, il s'agit de procéder à l'usinage

dans le silicium du corps d'épreuve d'un capteur, en s'inspirant

des géométries retenues pour les capteurs classiques mais

en procédant à une réduction

d'échelle très importante afin d'une part de minimiser

les coûts et d'autre part de permettre la réalisation sur un

même wafer d'un nombre important de microcapteurs ayant donc des caractéristiques

semblables puisque réalisés simultanément.

C'est cette seconde partie que nous allons examiner maintenant. En prenant pour

exemple la réalisation d'un capteur de pression.

les problèmes principaux

Deux problèmes principaux sont à résoudre. L'un est de

nature mécanique, il s'agit de pouvoir identifier le

positionnement relatif avec une précision de l'ordre du micron

d'un motif diffusé sur une face du wafer (pont de jauges) et du centre

de la membrane correspondante sur l'autre face du wafer. En d'autre termes pouvoir

retourner un wafer afin de procéder à son alignement

en vue d'un processus de masquage sur les deux faces et non comme dans

les composants électroniques sur une seule face.

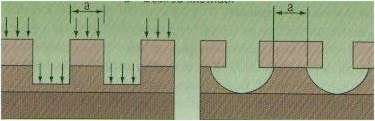

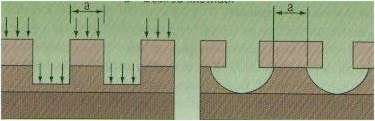

Le second problème concerne l'usinage lui-même. En microélectronique

classique on ouvre des fenêtres dans une couche d'oxyde de 1 µm

d'épaisseur, ici il va falloir usiner des motifs beaucoup plus importants

en épaisseur. Imaginons un wafer de 100 µm d'épaisseur dans

lequel nous avons l'obligation d'obtenir des membranes de 2mm de diamètre

et de 30 µm d'épaisseur. Définir par masquage des fenêtres

de 2mm de diamètre ne pose pas de problème insurmontable, mais

comment ensuite creuser dans cette fenêtre un puits de 70 µm de

profondeur? Et garantir surtout que le fond du puits sera plan

et parfaitement parallèle au plan

de l'autre face du wafer. Le problème est illustré par la figure

suivante.

Fig. décapage physique par plasma ou chimique (à droite)?

Fig. décapage physique par plasma ou chimique (à droite)?

les procédés de gravure

Plusieurs techniques ont été imaginées pour micro-usiner

le silicium :

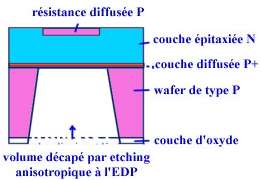

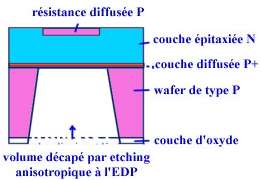

- historiquement l'une des premières réponses satisfaisantes

a consisté en la réalisation d'une structure

épitaxiale. On utilise un wafer de type P dopé P+ en

surface et l'on fait croître par épitaxie une couche d'épaisseur

équivalente à la membrane de type n dans laquelle on diffusera

les jauges de contraintes (résistances de type P). On procède

alors à la dissolution de la zone P selon le process dit P+

etch-stop. On a en effet découvert que l'EDP permettait de

procéder à un etching (ou gravure) anisotropique,

c'est à dire couche par couche en conservant donc sensiblement la

planéité initiale du wafer et la zone P+ arrête le décapage.

Cette méthode conduit à une uniformité de l'épaisseur

de la membrane à environ 1µm près, mais, d'autre part,

la solution d'attaque chimique employée est un poison et est très

délicate à recycler.

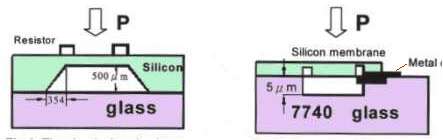

capteur de pression réalisé par décapage anisotropique

P+ etch-stop

capteur de pression réalisé par décapage anisotropique

P+ etch-stop

- Le second procédé utilise le même empilement de couche

épitaxiée N sur un substrat P mais exploite un

potentiel négatif pendant le décapage ce qui facilite

l'obtention d'un décapage uniforme par le biais d'une solution de

KOH.

- Le troisième procédé utilise, comme principe d'arrêt

du décapage, une couche faiblement dopée N-(<1017/cm3).

Dans ce cas le décapage est isotrope et peut être obtenu avec

HNA c'est à dire un mélange d'acide

fluorhydrique, nitrique et d'alcool dans la proportion 1:3:8. Il suffit

donc d'une couche épitaxiée N- sur le substrat

P ce qui réduit le nombre d'opérations et semble donc le procédé

le plus approprié.

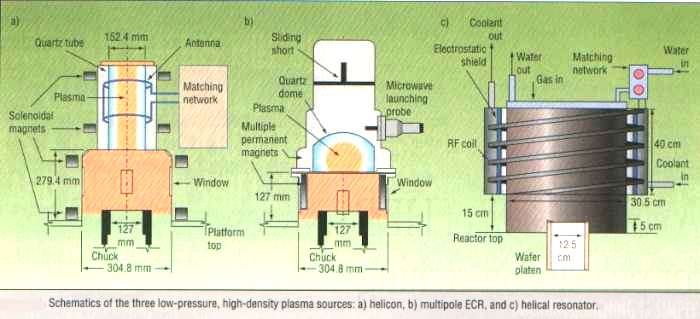

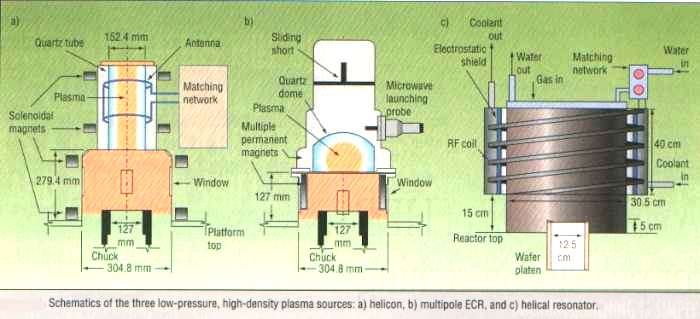

- Une autre procédure implique des moyens plus sophistiqués

c'est le décapage ionique qui présente

l'intérêt de l'anisotropie mais nécessite la génération

de faisceaux d'ions uniformes de grande section. La figure ci-dessous montre

quelques principes de dispositifs exploités pour créer de

telles sources de plasma.

Fig. diverses sources d'ions permettant un décapage anisotrope [doc.

Solid State Technology]

Fig. diverses sources d'ions permettant un décapage anisotrope [doc.

Solid State Technology]

packaging

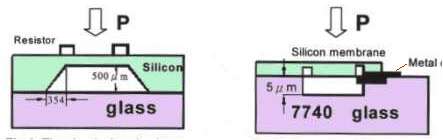

Les différents procédés de packaging (encapsulation) mis

en oeuvre dans la réalisation de capteurs de pression ont évidemment

comme objectif fondamental la protection du transducteur autant que l'obtention

d'un dispositif manipulable. Le verre de silice est souvent exploité

complémentairement au Si car on dispose de facilité de soudure

de l'un sur l'autre. L'exploitation du pyrex type 7740 a récemment ouvert

de nouvelles pistes technologiques. En effet ce matériau peut facilement

être lithogravé. La figure ci-dessous montre comment cela peut

conduire à une simplification des procédés de fabrication

de capteurs de pression.

Fig. procédés classique et innovant de packaging [Yang99]

Fig. procédés classique et innovant de packaging [Yang99]

Dans le second dispositif la membrane peut être obtenue par usinage mécanique

partiel et simplement ajustée chimiquement puisqu'on n'a besoin que d'une

membrane plane la cavité étant générée dans

le verre. On voit que cela permet de réduire la quantité de silicium

nécessaire et donc de miniaturiser encore plus le capteur. En outre il

est alors possible de monter la face supportant les jauges non à l'extérieur

mais à l'intérieur de la cavité ce qui facilite grandement

leur protection sans changer sensiblement les propriétés mécaniques.

Notons que la cavité peut aussi bien être sous vide (capeur absolu)

qu'à la pression atmosphérique "normale" (capteur relatif).

L'électronique

du futur : Une avancée majeure dans le développement des transistors

Une équipe de chercheurs de l'Institut National des Sciences des Matériaux

(NIMS) de Tsukuba et de l'Université de Tokyo a expérimenté

un nouveau type de transistor qui pourrait à terme constituer une nouvelle

génération de composants électroniques.

Une équipe de chercheurs de l'Institut National des Sciences des Matériaux

(NIMS) de Tsukuba et de l'Université de Tokyo a expérimenté

un nouveau type de transistor qui pourrait à terme constituer une nouvelle

génération de composants électroniques.

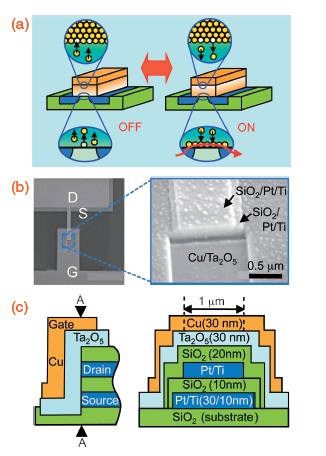

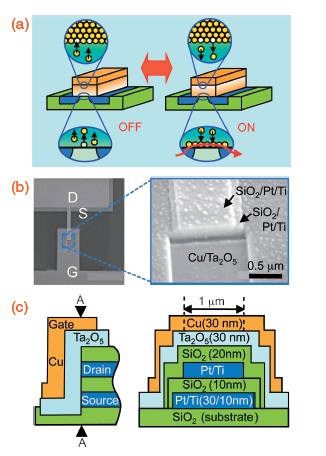

En effet, ce transistor

ne consomme que 1% de l'électricité utilisée par les

transistors actuels (pW) et est capable à la fois d'opérations

volatiles (l'information s'efface lors d'une interruption de l'alimentation

électrique, à la manière des mémoires RAM actuellement

utilisées dans les ordinateurs) et non-volatiles (l'information est

conservée même en cas d'interruption électrique, comme

c'est le cas dans les disques durs par exemple).high ON/OFF ratio [106 (volatile

operation) to 108 (nonvolatile operation)] et compatibilité technologique

avec les CMOS actuels.

Pour obtenir ces caractéristiques,

l'équipe de chercheurs s'est basée sur le contrôle du

courant, non pas dans un semi-conducteur comme c'est le cas dans un transistor

traditionnel, mais sur le canal conducteur généré par

le passage de l'état fondamental à l'état ionisé

d'atomes de cuivre composant la grille. Ce canal est formé

à l'interface entre la grille et un isolant qui relie la source et

le drain (voir figure). Lorsque la concentration de cations, qui dépend

de la tension de grille, atteint une certaine valeur, on observe une forte

variation de la conductivité, c'est-à-dire une transition isolant-conducteur.

Les applications potentielles

de cette recherche sont très nombreuses dans le domaine de l'électronique.

Au niveau du grand public, il serait par exemple possible de recharger très

rapidement son smartphone, dont l'autonomie aura été par ailleurs

grandement accrue. De plus, les opérations non-volatiles étant

possibles avec ce type de transistor, le temps d'allumage des machines électroniques

pourrait devenir extrêmement court (car la mémoire vive ne serait

pas effacée lors d'une coupure de l'alimentation électrique).

L'équipe de recherche

a déclaré que ces résultats permettent de progresser

vers une augmentation de l'efficacité des composants électroniques

jusqu'ici limitée par le problème de la consommation électrique.

Bien évidemment, cette technologie mettra encore quelques années

à arriver dans des produits grand public, l'équipe de recherche

commençant à peine les discussions de commercialisation avec

des entreprises.

légendes de la figure:

(a) situation conductrice ou non du dispositif. Les atomes ionisés forment

un chemin conducteur entre la source et le drain

(b) images du dispositif vu au microscope électronique

(c) section du dispositif montrant les différentes couches

Pour en savoir plus,

"Volatile/Nonvolatile Dual-Functional Atom Transistor" - HASEGAWA

Tsuyoshi et al. - Applied Physics Express 4 - 24/12/2010 - http://dx.doi.org/10.1143/APEX.4.015204

nouveautés 2013

La technologie continue à évoluer dans le sens de la nanominiaturisation.

Ainsi Intel va produire des circuits programmables pour Altera en technology

14 nm. Rappelons qu'en 1970 un transistor avait 2mm de côté,

ainsi en une quarantaine d'années le facteur diminution est d'environ

1OOOOO. Un composant à donc dorénavant une largeur inférieure

à la dizaine d'atomes.

J. Czochralski, Zeits.Phys. Chem., 92 (1917) pp 219.

L-J Yang & al., A new strategy to reduce the chip size of the bulk-machined

micro-sensors, Int. Congress Sensors 99, Nürnberg, may 1999, vol1 pp

397-402

J. Mavor, MOST integrated circuit engineering, IEE summer school, Edinburgh,

september 1972

Y. Legros, les semiconducteurs, Eyrolles (Paris), 1974.

A. Vapaille, R. Castagné, Dispositifs et circuits intégrés

semiconducteurs, Dunod (Paris), 1987.

R.C. Dorf, The Electrical Engineering Handbook, CRC Press (Boca Raton, Fla),

1993.

Jean-Baptiste Waldner, Nano-informatique et Intelligence Ambiante,

Hermès Science, London, 2006, ISBN 2746215160.

BE Japon numéro

560 (7/01/2011) - Ambassade de France au Japon / ADIT - http://www.bulletins-electroniques.com/actualites/65529.htm

International Technology Roadmap for Semiconductors (2009) [http://www.itrs.net/Links/2009ITRS/].

Une équipe de chercheurs de l'Institut National des Sciences des Matériaux

(NIMS) de Tsukuba et de l'Université de Tokyo a expérimenté

un nouveau type de transistor qui pourrait à terme constituer une nouvelle

génération de composants électroniques.

Une équipe de chercheurs de l'Institut National des Sciences des Matériaux

(NIMS) de Tsukuba et de l'Université de Tokyo a expérimenté

un nouveau type de transistor qui pourrait à terme constituer une nouvelle

génération de composants électroniques.